高速PCB设计中的信号完整性挑战与应对策略

在快速发展的手游市场中,高速PCB设计扮演着至关重要的角色,它不仅影响着游戏的流畅度,还直接关系到玩家体验的好坏,我们就来深入探讨高速PCB设计中信号完整性的常见问题,并为你提供权威的解决方案。🎮

一、信号衰减:速度与质量的双重考验

在高速PCB设计中,信号衰减是一个不容忽视的问题,随着信号频率的提升,传输线上的损耗也会相应增加,导致信号质量下降,这种衰减不仅会影响游戏的响应速度,还可能引发数据错误,从而影响玩家的游戏体验,为了应对这一挑战,设计师们需要采用低损耗的材料和优化的传输线设计,以确保信号在传输过程中的稳定性和完整性。📡

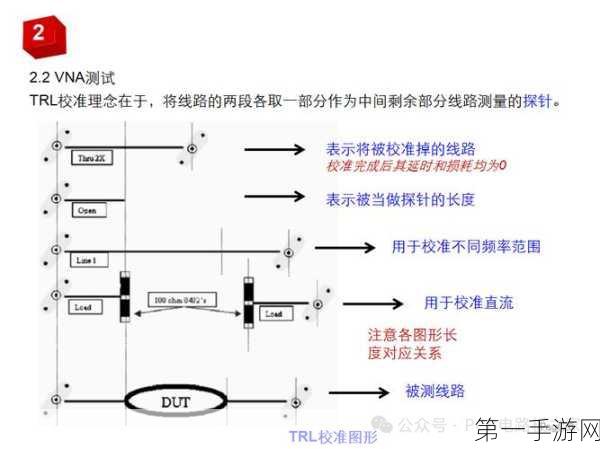

二、阻抗不匹配:引发反射的罪魁祸首

阻抗不匹配是高速PCB设计中另一个常见的信号完整性问题,当信号在传输线上遇到阻抗突变时,会发生反射现象,导致信号波形失真,这种失真不仅会降低信号的传输效率,还可能引发数据冲突,影响游戏的正常运行,为了解决这个问题,设计师们需要仔细规划传输线的阻抗,确保整个传输路径上的阻抗保持一致,还可以采用终端匹配电阻等方法来减少反射。🔄

三、串扰与噪声:干扰信号的双重打击

在高速PCB设计中,串扰和噪声也是影响信号完整性的重要因素,串扰是指相邻传输线之间的信号相互干扰,而噪声则是由外部环境引入的干扰信号,这两种干扰都会导致信号质量的下降,从而影响游戏的稳定性和流畅度,为了降低串扰和噪声的影响,设计师们需要采用合理的布线策略,如增加传输线之间的距离、使用屏蔽线等,还可以采用滤波器和去耦电容等元件来抑制噪声。🔇

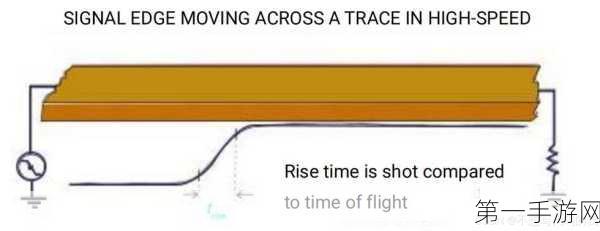

四、时序问题:速度与同步的较量

时序问题是高速PCB设计中另一个需要关注的重点,在高速数据传输中,信号的传输延迟和时钟偏差都可能引发时序问题,导致数据无法正确同步,这种同步问题不仅会影响游戏的流畅度,还可能引发数据丢失和错误,为了解决这个问题,设计师们需要仔细规划时钟树的布局和布线,确保时钟信号的稳定性和一致性,还可以采用DLL(延迟锁定环)和PLL(相位锁定环)等时钟同步技术来优化时序性能。🕒

五、实战案例:手游大作中的高速PCB设计

以某款热门手游为例,该游戏在高速PCB设计中采用了先进的材料和工艺,以确保信号的完整性和稳定性,通过采用低损耗的传输线和优化的阻抗设计,该游戏成功降低了信号衰减和反射的影响,通过合理的布线策略和滤波器的使用,该游戏也有效抑制了串扰和噪声的干扰,该游戏在高速数据传输中实现了出色的时序性能,为玩家提供了流畅而稳定的游戏体验。🎉

六、权威数据:手游市场中的高速PCB设计趋势

根据最新的手游市场研究报告,随着游戏技术的不断进步和玩家需求的日益提升,高速PCB设计在手游中的应用越来越广泛,数据显示,采用高速PCB设计的手游作品在流畅度、稳定性和玩家满意度等方面均表现出色,随着5G、云计算等技术的不断发展,高速PCB设计在手游中的应用前景将更加广阔。📈

高速PCB设计中的信号完整性问题是影响手游性能和玩家体验的关键因素之一,通过采用先进的材料和工艺、合理的布线策略和优化的时钟同步技术,我们可以有效应对这些挑战,为玩家提供流畅而稳定的游戏体验,在未来的手游市场中,高速PCB设计将发挥更加重要的作用,推动游戏技术的不断进步和发展。🚀